GERY022 December 2024 AMC0106M05 , AMC0106M25 , AMC0136 , AMC0311D , AMC0311S , AMC0386 , AMC0386-Q1 , AMC1100 , AMC1106M05 , AMC1200 , AMC1200-Q1 , AMC1202 , AMC1203 , AMC1204 , AMC1211-Q1 , AMC1300 , AMC1300B-Q1 , AMC1301 , AMC1301-Q1 , AMC1302-Q1 , AMC1303M2510 , AMC1304L25 , AMC1304M25 , AMC1305M25 , AMC1305M25-Q1 , AMC1306M05 , AMC1306M25 , AMC1311 , AMC1311-Q1 , AMC131M03 , AMC1336 , AMC1336-Q1 , AMC1350 , AMC1350-Q1 , AMC23C12 , AMC3301 , AMC3330 , AMC3330-Q1

- 1

- Einführung

- Einführung in die isolierte Signalkette

- Auswahlb?ume

-

Strommessung

- Shunt-Widerstandsauswahl für isolierte Datenwandler

- Designüberlegungen für die isolierte Strommessung

- Isolierte Strommessschaltung mit ±50?mV-Eingang und unsymmetrischem Ausgang

- Isolierte Strommessschaltung mit ±50?mV-Eingang und Differenzausgang

-

Isolierte Strommessschaltung mit ±250?mV Eingangsbereich und unsymmetrischer Ausgangsspannung

- Designziele

- Designbeschreibung

- Designhinweise

- Designschritte

- Design-Simulationen

- DC-Simulationsergebnisse

- Ergebnisse der AC-Simulation im geschlossenen Regelkreis

- Ergebnisse der Transienten-Simulation

- Designreferenzen

- Design empfohlener isolierter Verst?rker

- Design Alternativer Isolierter Verst?rker

- Isolierter Strommessschaltkreis mit ±250?mV-Eingang und Differenzausgang

- Isolierter überstromschutzschaltkreis

- Anschluss eines Differenzialausgangsverst?rkers (isoliert) an einen A/D-Wandler mit unsymmetrischem Eingang

- Verwendung von AMC3311 zur Stromversorgung des AMC23C11 für isolierte Sensorik und Fehlererkennung

- Isolierte Strommessschaltung mit Frontend-Verst?rkungsstufe

- Genauigkeitsvergleich von isolierten Shunt- und Geschlossener Regelkreis-Strommessungen

-

Spannungserfassung

- Maximieren Sie die Leistungswandlung und die Wirksamkeit der Motorsteuerung durch isolierte Spannungserfassung

- H?here Genauigkeit und Leistung mit integrierten isolierten Verst?rkern und Modulatoren mit Hochspannungswiderstand

- Isolierte Verst?rker mit differenziellen, unsymmetrischen Festverst?rkern und ratiometrischen Ausg?ngen für Spannungssensoranwendungen

- Isolierte Spannungsmessschaltung mit ±250?mV-Eingang und Differenzausgang

- Split-Tap-Verbindung für isolierte Line-to-Line-Spannungsmessung mit AMC3330

- ±12 V-Spannungssensorschaltung mit isoliertem Verst?rker und pseudo-differenziellem Eingang SAR-ADC

- ±12 V-Spannungssensorschaltung mit isoliertem Verst?rker und SAR-ADC mit Differenzeingang

- Isolierter Schaltkreis zur Erkennung von Unter- und überspannung

- Isolierter Nulldurchgangsschaltkreis

- Isolierter Spannungssensorschaltkreis mit ±480?V und Differenzausgang

-

EMI-Leistung

-

Beste EMI-Leistung in ihrer Klasse bei Strahlungsemissionen mit isolierten Verst?rkern

- Beste EMI-Leistung in ihrer Klasse bei Strahlungsemissionen mit isolierten Verst?rkern

- Einführung

- Aktuelle Generation von isolierten Verst?rkern von Texas Instruments Strahlungsemissionenleistung

- Frühere Generationen von isolierten Verst?rkern von Texas Instruments strahlen St?rstrahlungsleistung aus

- Fazit

- Quellennachweise

- Bew?hrte Methoden zur D?mpfung von EMI-St?rstrahlungen der AMC3301-Familie

-

Beste EMI-Leistung in ihrer Klasse bei Strahlungsemissionen mit isolierten Verst?rkern

-

Endger?te

- Vergleich von isolierten Shunt- und Hall-basierten Strommessl?sungen in Hybrid- und Elektrofahrzeugen

-

Designüberlegungen für die Strommessung in DC-EV-Ladeanwendungen

- Kurzfassung

- Einführung

-

Strommessung in AC/DC-Wandlern

- Grundlegende Hardware und Steuerungsbeschreibung von AC/DC

- Punkt A und B – AC/DC AC-Phasenstrommessung

- Punkt C und D – AC/DC DC-Link-Strommessung

- Zusammenfassung der positiven und negativen Punkte an den Punkten A, B, C1/2 und D1/2 sowie Produktvorschl?ge

- Strommessung in DC/DC-Wandlern

- Fazit

- Quellennachweise

-

Verwendung isolierter Komparatoren zur Fehlererkennung in Elektromotorantrieben

- Einführung

- Einführung in Elektromotorantriebe

- Verst?ndnis von Fehlerereignissen in Elektromotorantrieben

- Zuverl?ssige Erkennung und Schutz in Elektromotorantrieben

- Anwendungsfall Nr. 1: Bidirektionale Phasenüberstromerkennung

- Anwendungsfall Nr. 2: DC+-überstromerkennung

- Anwendungsfall Nr. 3: DC–überstrom- oder Kurzschlusserkennung

- Anwendungsfall Nr. 4: DC-Link (DC+ zu DC-) überspannungs- und Unterspannungserkennung

- Anwendungsfall Nr. 5: übertemperaturerkennung des IGBT-Moduls

- Diskrete DESAT für optokompatible isolierte Gate-Treiber UCC23513 in Motorantrieben

- Isolierte Spannungserfassung in AC-Motorantrieben

- Hochleistungsf?hige isolierte Strom- und Spannungsmessung in Server-Netzteilen

-

Zus?tzliche Referenzdesigns/Schaltkreise

- Entwicklung einer Bootstrap-Ladepumpen-Stromversorgung für einen isolierten Verst?rker

-

Taktflankenverz?gerungskompensation mit isolierten Modulatoren Digitale Schnittstelle zu MCUs

- Zusammenfassung

- Einführung

- Design-Herausforderung durch Timing-Spezifikationen für digitale Schnittstellen

- Designansatz mit Taktflankenverz?gerungskompensation

- Test und Validierung

- Fazit

- Quellennachweise

- Verwendung von AMC3311 zur Stromversorgung des AMC23C11 für isolierte Sensorik und Fehlererkennung

| ISO224 Eingangsspannung | ISO224 AUSGANG (VOUTP – VOUTN) | ADS7142 Eing?nge (pseudodifferenziell) | ADS7142 Digital-Ausgang |

|---|---|---|---|

| 12V | 4V | 3,3 V | FFFH |

| -12V | -4V | 0V | 000H |

| Stromversorgungen und Referenzspannungen | |||

|---|---|---|---|

| VDD1 | VDD2 und Vcc | AVDD | GND |

| 4,5 V – 18 V | 5V | 3,3 V | 0V |

Designbeschreibung

Dieser Schaltkreis führt eine isolierte Spannungsmessung von ±12 V mit dem isolierten ISO224-Verst?rker, TLV9002-Operationsverst?rker und dem ADS7142-SAR-ADC durch. Der ISO224 kann unsymmetrische Signale von ±12 V mit einer festen Verst?rkung von ? V/V messen und erzeugt eine isolierte Differenzausgangsspannung von ±4 V mit einer Gleichtaktspannung von VDD2 / 2. Kanal 1 der TLV9002 konditioniert den Ausgang des ISO224, um zum Eingangsbereich des ADS7142 zu passen, w?hrend Kanal 2 den ISO224 ausfallsicheren Ausgang überwacht. Der ADS7142 ist ein zweikanaliger ADC mit einer Vollausschlag-Eingangs- und Referenzspannung von AVDD, die von 1,65 V bis 3,6 V reichen kann. Für diese Cookbook-Schaltung wird der ADS7142 Zweikanal-Eingang in einer pseudo-differenziellen Konfiguration verwendet, die es erm?glicht, sowohl positive als auch negative Signale vom ISO224 zu messen . Dieser Schaltkreis eignet sich für viele industrielle Hochspannungsanwendungen, wie Zugsteuerungs- und Managementsysteme, Analogeingangsmodule und Inverter und Motorsteuerung. Die Gleichungen und Erkl?rungen zur Komponentenauswahl in diesem Design k?nnen auf der Grundlage der Anforderungen und Systemspezifikationen des Endger?tes angepasst werden.

Spezifikationen

| Spezifikation | Berechnet | Simuliert |

|---|---|---|

| Einschwingverhalten des transienten ADC-Eingangs bei 140 kSPS | 403 μV | 88 μV |

| Konditionierter Signalbereich | 0 V–3,3 V | 0 V–3,3 V |

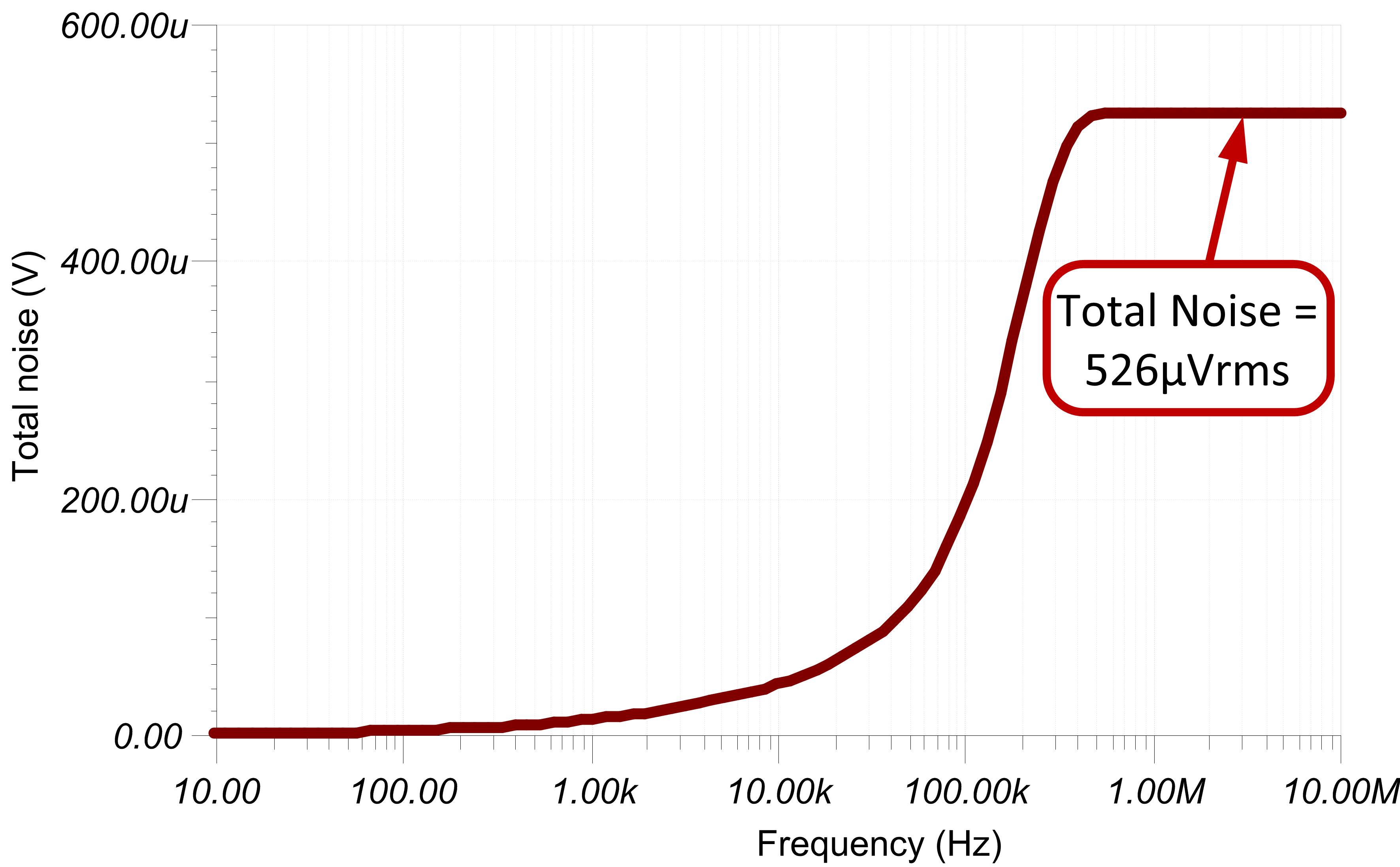

| Rauschen (am Eingang) | 262 μVRMS | 526 μVRMS |

| Geschlossener Regelkreis-Bandbreite | 175 kHz | 145 kHz |

Designhinweise

- Der ISO224 wurde aufgrund des gro?en Eingangsbereichs, der flexiblen Leistungskonfiguration und der hohen Genauigkeit ausgew?hlt.

- Der ADS7142 wurde aufgrund des sehr geringen Stromverbrauchs, des hohen Integrationsgrads, flexibler Stromversorgungskonfigurationen und der geringen Gr??e ausgew?hlt.

- Der Operationsverst?rker TLV9002 wurde für die Kostenoptimierung, Konfigurationsoptionen und geringe Gr??e ausgew?hlt.

- W?hlen Sie Quellen mit niedriger Impedanz und geringem Rauschen für AVDD, VCM und den pseudo-differenziellen Eingang an AINN aus, der die Gleichtaktspannung des A/D-Wandlers festlegt.

- Ermitteln Sie den Gesamtbereich und die Gleichtaktspezifikationen des A/D-Wandlers. Dies wird in der Komponentenauswahl besprochen.

- W?hlen Sie einen COG-Kondensator für CFILT, um Verzerrungen zu minimieren.

- Um die beste Leistung zu erzielen, sollten Sie einen Schichtwiderstand von 0,1 % 20 ppm/°C für RFILT1,2 oder besser verwenden, um Verzerrungen zu minimieren.

- In Verstehen und Kalibrieren von Offset und Verst?rkung für ADC-Systeme werden Methoden zur Fehleranalyse erl?utert. Unter dem Link finden Sie Methoden zur Minimierung von Verst?rkungs-, Offset-, Drift- und Rauschfehlern.

- In der Schulungsvideoreihe TI Precision Labs – ADCs werden Methoden zur Auswahl der Ladeschaltkreise RFILT und CFILT behandelt. Diese Komponentenwerte sind von der Verst?rkerbandbreite, der Abtastrate des Datenwandlers und dem Design des Datenwandlers abh?ngig. Die hier gezeigten Werte bieten eine gute Einschwingleistung und AC-Leistung für den Verst?rker und den Datenwandler in diesem Beispiel. Wenn das Design ge?ndert wird, muss ein anderer RC-Filter ausgew?hlt werden. Eine Erkl?rung zur Auswahl des RC-Filters für optimale Einschwingeigenschaften und beste AC-Leistung finden Sie in Einführung zur Auswahl der SAR-ADC-Frontend-Komponenten.

Komponentenauswahl

- W?hlen Sie einen isolierten Verst?rker anhand des Eingangsspannungsbereichs aus, und legen Sie die Ausgangsgleichtaktspannung und den Ausgangsspannungsbereich fest:

Die ISO224-Netzteile k?nnen 4,5 V bis 18 V für die Highside-Stromversorgung und 4,5 V bis 5,5 V für die Low-Side-Stromversorgung sein. Der ISO224 besitzt einen unsymmetrischen Eingangsbereich von ±12 V mit einer festen Verst?rkung von ?V/V und ergibt einen Differenzausgang von ±4 V bei einer Gleichtaktspannung von VDD2 / 2, 2,5 V für dieses Beispiel:

- W?hlen Sie einen ADC mit geringer Gr??e und geringem Stromverbrauch:

Der ADS7142 ist ein kleiner, energieeffizienter Zweikanal-ADC, der in einer pseudodifferenziellen Konfiguration verwendet werden kann. Der maximale Eingangsbereich wird durch die Referenzspannung festgelegt und ist gleich AVDD, 3,3 V für dieses Beispiel:

Ermitteln Sie die erforderliche Gleichtaktspannung des A/D-Wandlers für pseudodifferenzielle Messungen:

- W?hlen Sie einen Operationsverst?rker aus, der den differenziellen 2,5 V-Gleichtaktausgang des ISO224 mit ±4 V in den 3,3 V pseudodifferenziellen 1,65 V-Gleichtakteingang des ADS7142 umwandeln kann. Darüber hinaus sollte ein Operationsverst?rker mit einem zweiten Kanal gew?hlt werden, der die ausfallsichere Ausgangsfunktion des ISO224 überwachen kann.

Der TLV9002 ist ein 2-kanaliger Verst?rker mit Rail-to-Rail-Eingang und -Ausgang, der für kostensensible und kompakte Anwendungen optimiert ist.

Kanal 1 wird verwendet, um den ±4 V Differenzial-, 2,5 V Gleichtakt-Ausgang des ISO224 in einen 3,3 V-Spitzen-Pseudo-Differenzialausgang mit einer Gleichtaktspannung von 1,65 V zu konvertieren. Bei R1 = R4 und R2 = R3 wird die übertragungsfunktion durch folgende Gleichung eingestellt:

Das Signal muss von ±4 V auf 3,3 V konvertiert werden, das hei?t, das Signal muss um den Faktor 3,3 V / ±4 V = 3,3 V / 8 V reduziert werden. Wird VCM durch den zuvor berechneten Wert 1,65 V ersetzt und R2 und R3 auf 10 kΩ gesetzt, ergeben sich die folgenden Gleichungen:

Das L?sen nach R1 und R4 ergibt Werte von 4.125 kΩ.

Weitere Informationen zu diesem Thema finden Sie im Anwendungshinweis Anbindung eines (isolierten) Verst?rkers mit Differenzausgang an einen A/D-Wandler mit unsymmetrischem Eingang.

Kanal 2 des TLV9002 wird zur überwachung der ausfallsicheren Ausgangsfunktion des ISO224 verwendet. Die ausfallsichere ISO224-Ausgangsfunktion wird aktiviert, wenn unabh?ngig vom Eingangssignal am VIN-Kontakt die High-Side-Stromversorgung (VDD1) fehlt. Der TLV9002-Kanal-2-Ausgang (VCOMP) wird an einen GPIO-Port des Systemcontrollers eingespeist und wird immer dann hochgesetzt, wenn die ausfallsichere Ausgangsfunktion aktiv ist. Weitere Details finden Sie im Anwendungshinweis zur Funktion Fail-Safe Output.

- W?hlen Sie R1FILT, R2FILT, und CFILT für das Einschwingverhalten des Eingangssignals und der Abtastrate von 140 kSPS:

Refine the RFILT and CFILT Values ist ein Video von TI Precision Labs, das die Methodik zur Auswahl von RFILT und CFILT zeigt. Der endgültige Wert von 1,1 kΩ und 330 pF lag deutlich unter einem halben niedrigstwertigen Bit (LSB) innerhalb des Erfassungsfensters.

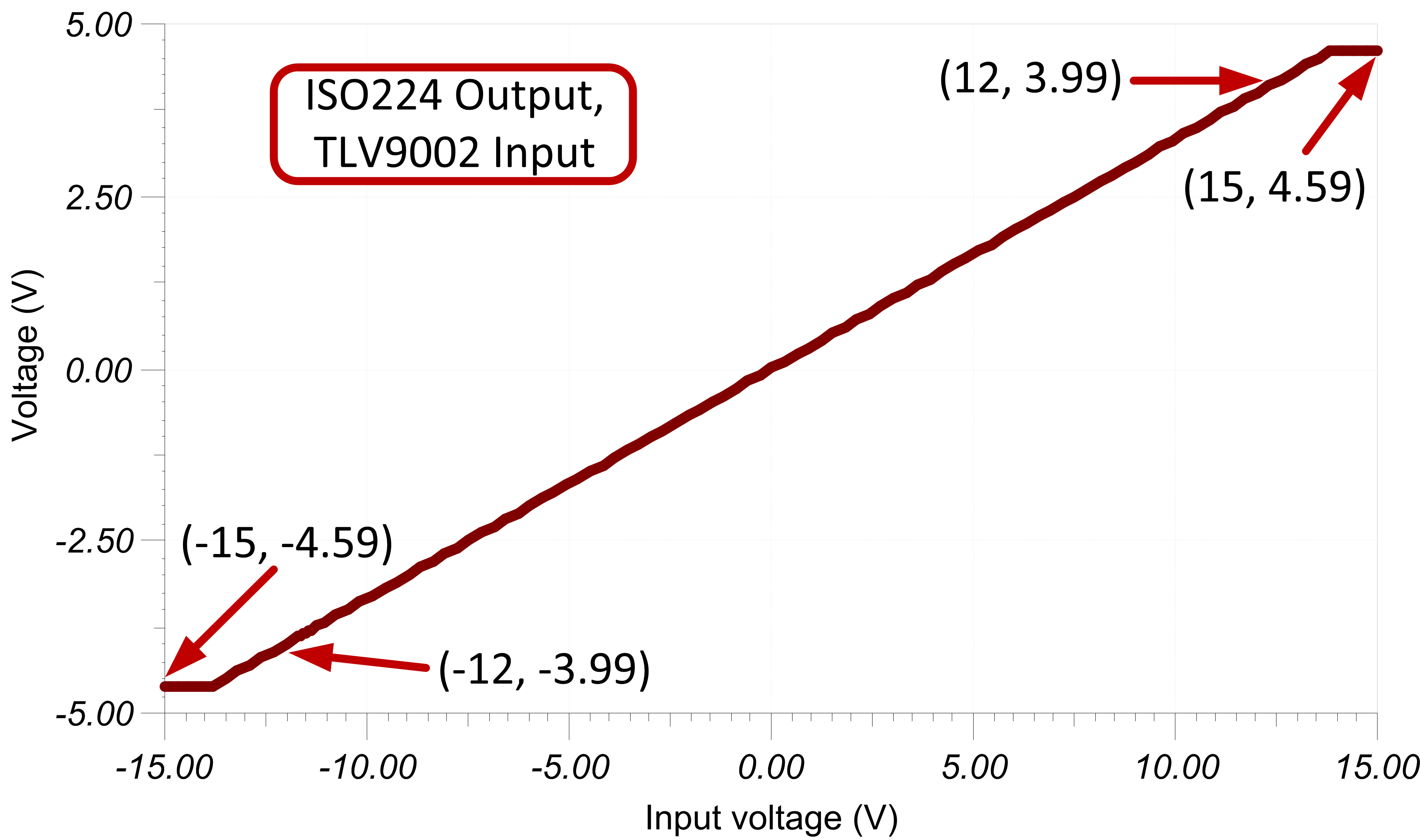

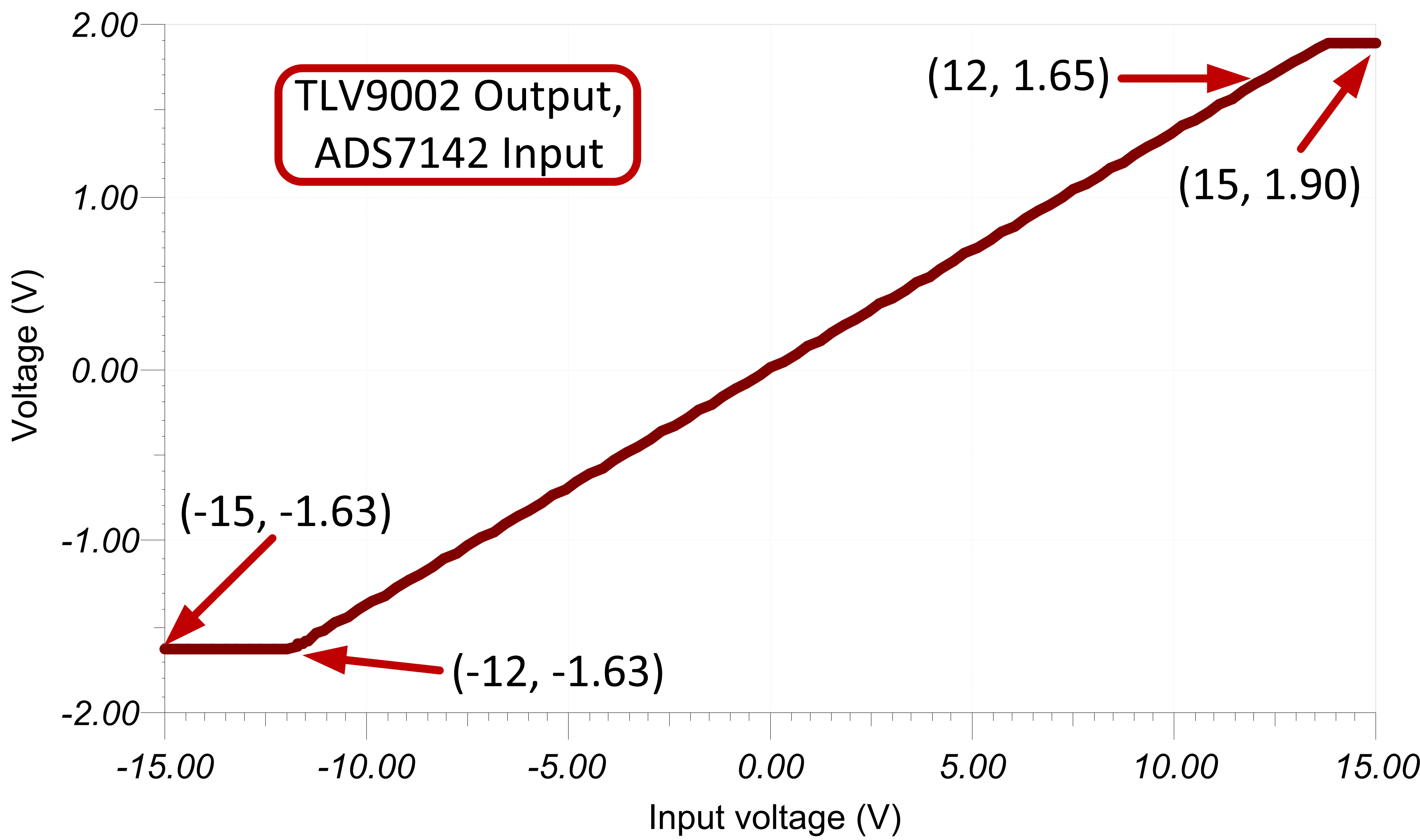

DC-übertragungskennlinie

Die folgenden Abbildungen zeigen die simulierten Eing?nge des TLV9002 und des ADS7142 von einem ±15 V-Eingangssignal an den ISO224. Der ISO224 hat ein lineares Ausgangssignal von ±VIN / 3. Die Eingangsspannung des TLV9002 ist im ersten Diagramm zu sehen. Das zweite Diagramm zeigt, dass der TLV9002 die Verst?rkung um VIN / 2,43 weiter reduziert und den Gleichtakt auf 1,65 V verschiebt. Dies führt zu einem vollst?ndigen Eingangssignal von ±12 V unter Verwendung des Vollausschlagsbereichs (FSR) von 0 V bis 3,3 V des A/D-Wandlers mit AVDD = VREF = 3,3 V.

Die folgende übertragungsfunktion zeigt, dass die Verst?rkung der ISO224 und TLV9002 1/7,28 V/V betr?gt

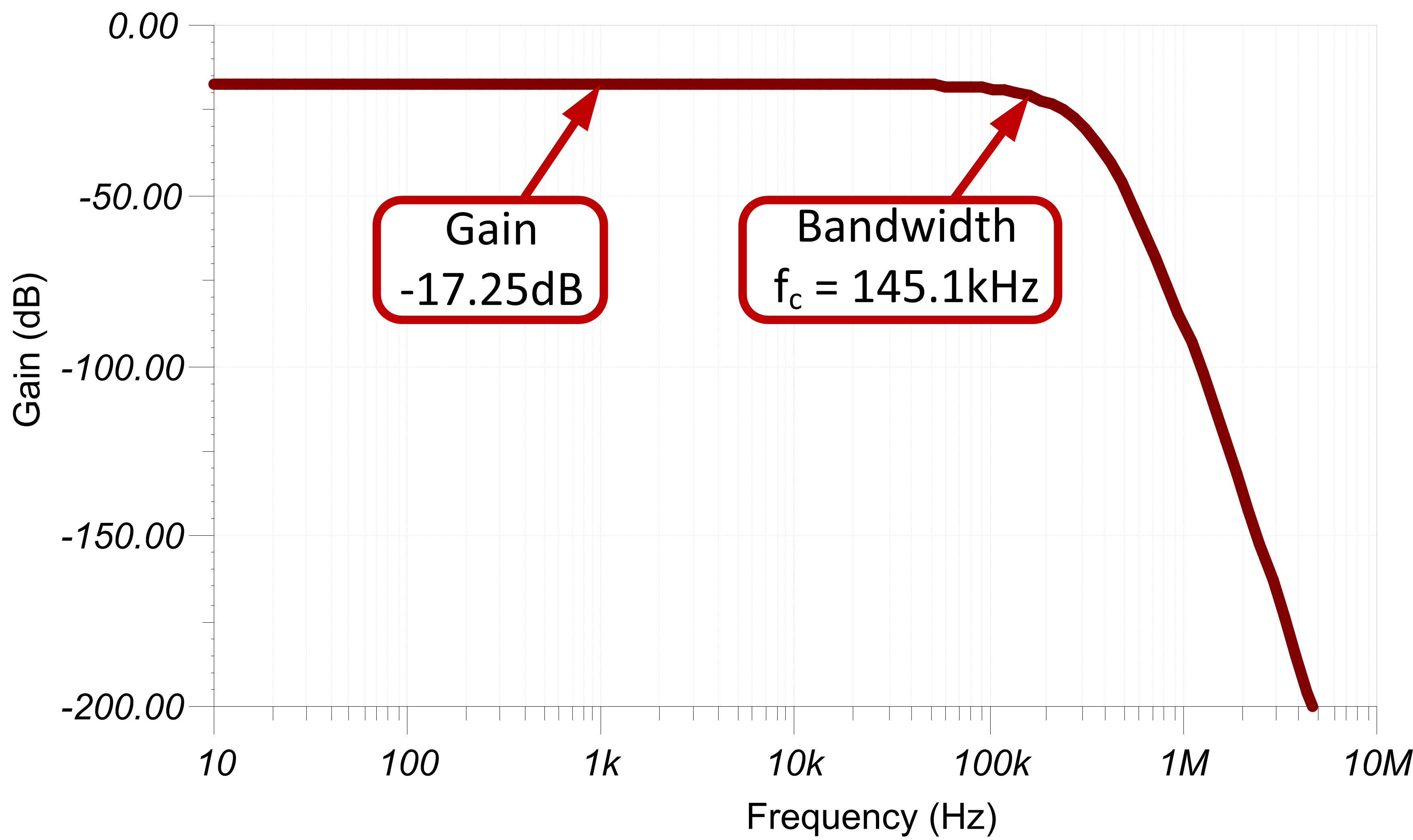

AC-übertragungskennlinie

Die simulierte Bandbreite der Signalkette betr?gt ca. 145 kHz und die Verst?rkung betr?gt -17,25 dB, was einer linearen Verst?rkung von ca. 0,137 V/V entspricht (D?mpfungsverh?ltnis 1/7,28 V/V). Dies entspricht der erwarteten Verst?rkung des Systems.

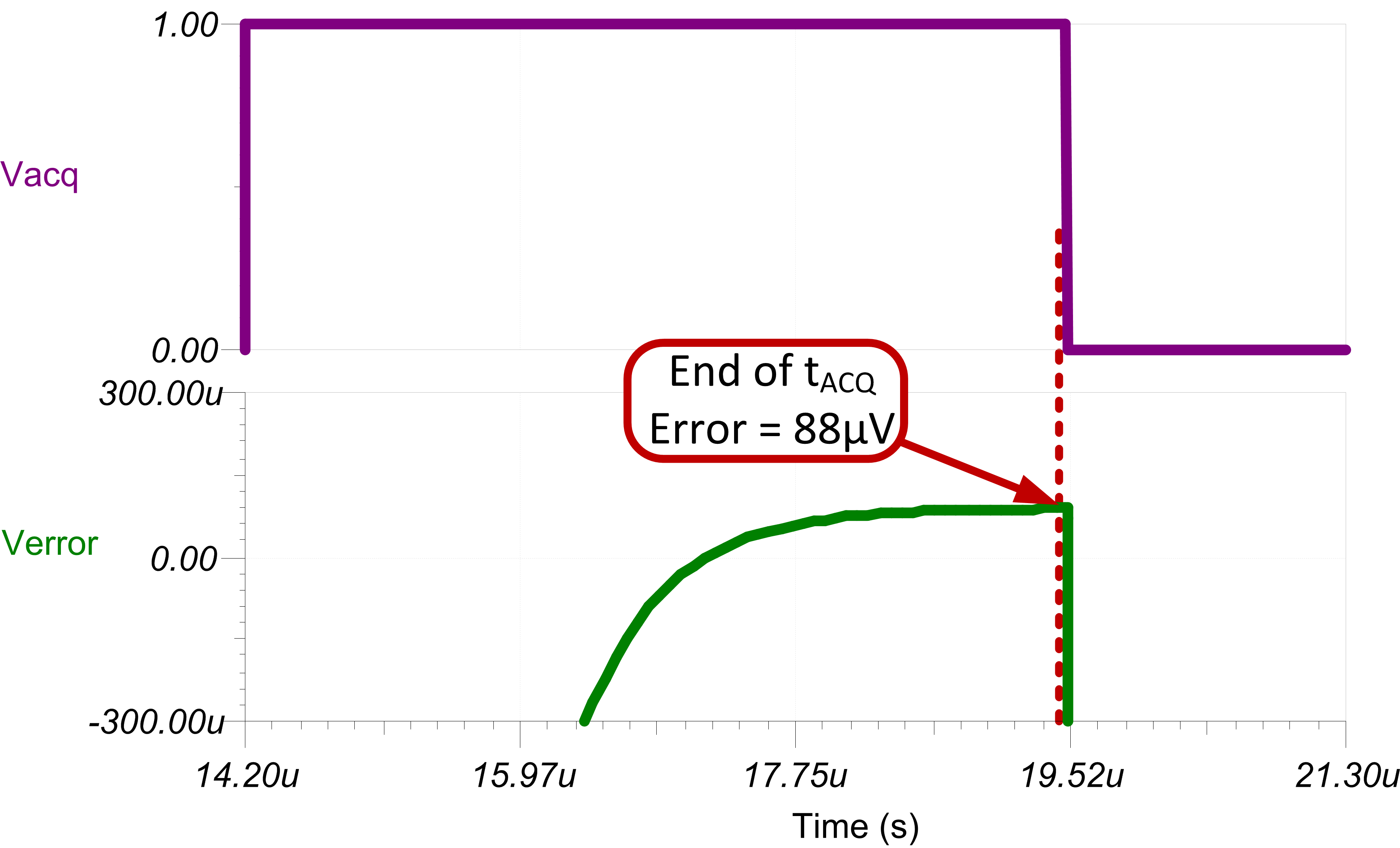

Simulation der Einschwingung des ADC-Eingangs bei Transienten

Die folgende Simulation zeigt die Ergebnisse des Einschwingvorgangs bei einer Erfassungszeit von 5.3 μs. Die Rauschleistung 88 μV liegt deutlich innerhalb der 0,5 × LSB-Grenze von 403 μV. Detaillierte theoretische Informationen zu diesem Thema finden Sie unter Verfeinern der Rfilt- und Cfilt-Werte.

Rauschsimulation

Das simulierte Rauschen am Eingang des A/D-Wandlers ist gr??er als das erwartete berechnete Rauschen. Der Grund für diesen Unterschied ist eine Rauschüberh?hung im Simulationsmodell, die nicht in der Berechnung enthalten ist. Die folgenden Gleichungen zeigen, dass das Rauschen von ISO224 die Signalkette dominiert und dass das Rauschen von TLV9002 vernachl?ssigbar ist. Detaillierte Informationen zu diesem Thema finden Sie unter Berechnen des Gesamtrauschens für ADC-Systeme.

Designreferenzen

Eine umfassende Schaltkreisbibliothek von TI finden Sie in Analog Engineer's Circuit Cookbooks.

Link zu Schlüsseldateien

TINA-Dateien für isoliertes Design: SBAC226

Design vorgestellter Bausteine

| Baustein | Wichtigste Leistungsmerkmale | Link | ?hnliche Bausteine: |

|---|---|---|---|

| ISO224 | Unsymmetrischer Eingangsbereich von ±12 V, feste Verst?rkung von ? ±, Differenzausgang 4 V, Ausgangsgleichtaktspannung von 2,5 V, Highside-Stromversorgung 4,5 V bis 18 V, Low-Side-Stromversorgung 4,5 V bis 5,5 V, Eingangs-Offset: ±5 mV bei 25 Grad Celsius, max. ±42 μV/ Grad Celsius, Verst?rkungsfehler: ±0,3 % bei 25 Grad Celsius, max. ±50 ppm Grad Celsius, Nichtlinearit?t: Maximal ±0,01 %, ±1 ppm/°C, hohe Eingangsimpedanz von 1.25 MΩ. | ISO224 | www.ti.com/isoamps |

| ADS7142 | Zweikanaliger, Full-Scale-Eingangsbereich und Referenzsatz von AVDD, standardm??ig 12-Bit-Leistung, 16-Bit-Leistung mit Hochpr?zisionsmodus, sehr geringer Stromverbrauch von 0.45 μA bei 600 SPS. | ADS7142 | https://www.ti.com/PrecisionADCs |

| TLV9002 | Zweikanaliger Verst?rker, Rail-to-Rail-Eingang und -Ausgang, geringes Breitbandrauschen von 2727 nV/√ Hz, niedrige Eingangs-Offsetspannung von ±0,04 mV. | TLV9002 | https://www.ti.com/opamps |